对于任何一个硬件模块的设计,首先第一步都是要先了解硬件本身后,再开始程序的软件设计。而由于DM9000的芯片文档内容很多,要驱动好网卡,需要很长时间,特别对于新手比较困难,所以可以参考linux内核代码中的网卡驱动程序,将其移植到裸机程序当中。下面将就ok6410,介绍DM9000裸机程序驱动的详细过程,并且完成arp协议的程序设计。

1. DM9000硬件接口

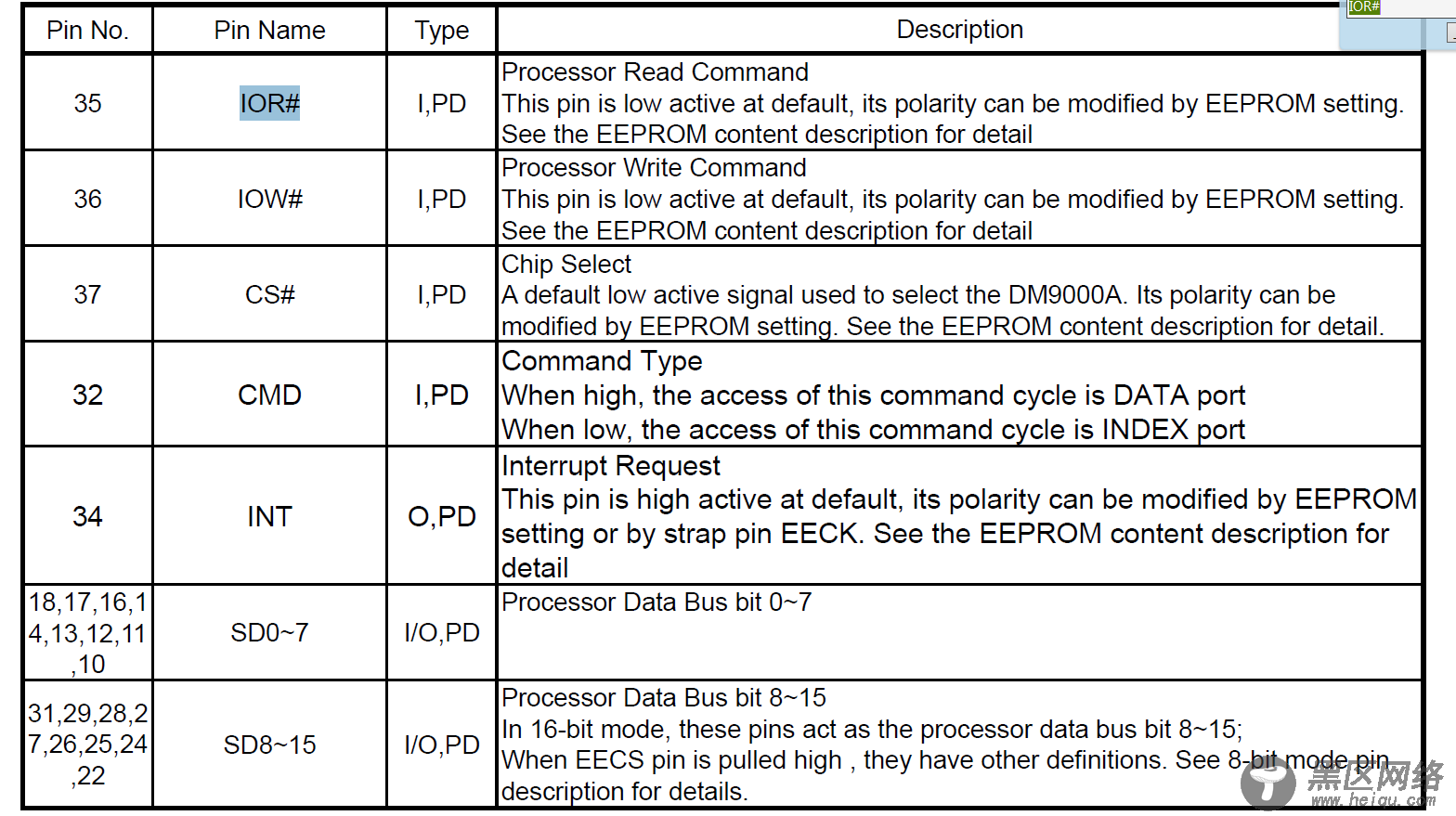

打开ok6410的底板原理图可以看到DM9000和ok6410的硬件接口,通过DM9000的文档大概浏览可知一些比较重要的引脚接口,如图:

再参考ok6410的核心板原理图可以很清楚的知道硬件接口对应的管脚:

SD0~SD15:DATA0~DATA15:XM0DATA0~XM0DATA15

CMD:ADDR2:XM0ADDR2

INT:IRQ_LAN:GPN7

IOR:OEN:XM0OEN

IOW:WEN:XM0WEN

CS:CSN1:XM0CSN1

从上面一些管脚的对应关系,可能很难理解控制的方式,这和GPIO等一些模块的裸机程序时有很大的不同。在6410芯片手册中搜索关键字,对于初学者,也很难了解到各个引脚的关系。但是通过网上的资料还是可以知道DM9000接口,接在了ROM1的控制模块中,ok6410并没有接ROM。这样就可以很清楚的知道以下的关系

DATA0~DATA15:ROM1的数据总线

ADDR2:ROM1的地址总线的第二位

IRQ_LAN:中断接口

OEN:nOE

WEN:nWE

CSN1:XM0CSn

这样对DM9000模块的读写相当于对ROM的读写了,关键的是CMD的引脚即ADDR2。

当CMD为1时DATA0~DATA15为数据总线

当CMD为0时DATA0~DATA15为地址总线。

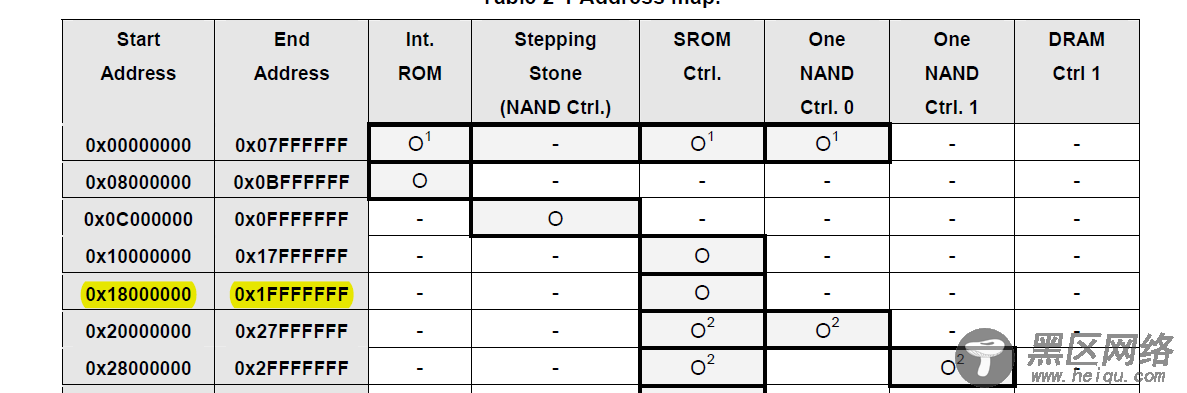

通过ok6410手册可以得出ROM1的起始地址为:0x18000000

2. DM9000程序设计

2.1 初始化读写时序

通过时序图配置以下寄存器

void cs_init()

{

SROM_BW &= (~(0xf<<4));

SROM_BW |= (0x1<<4);

SROM_BC1 =(0<<0)|(0x2<<4)|(0x2<<8)|(0x2<<12)|(0x2<<16)|(0x2<<24)|(0x2<<28);

}

2.2 读写操作函数

#define DM_ADD (*((volatile unsigned short *)0x18000000))

#define DM_DAT (*((volatile unsigned short *)0x18000004))

void dm9000_reg_write(u16 reg,u16 data)

{

DM_ADD = reg;

DM_DAT = data;

}

u8 dm9000_reg_read(u16 reg)

{

DM_ADD = reg;

return DM_DAT;

}

由硬件接口分析可知CMD即ROM1的地址总线的第二位,为1时为数据总线,为0是为地址总线,从而可以按上宏定义进行读写。

2.3 DM9000初始化

参考linux内核的DM9000驱动程序,可以清楚了解初始化的具体步骤

void dm9000_reset()

{

dm9000_reg_write(DM9000_GPCR, GPCR_GPIO0_OUT);

dm9000_reg_write(DM9000_GPR, 0);

dm9000_reg_write(DM9000_NCR, (NCR_LBK_INT_MAC | NCR_RST));

dm9000_reg_write(DM9000_NCR, 0);

dm9000_reg_write(DM9000_NCR, (NCR_LBK_INT_MAC | NCR_RST));

dm9000_reg_write(DM9000_NCR, 0);

}

void dm9000_probe(void)

{

u32 id_val;

id_val = dm9000_reg_read(DM9000_VIDL);

id_val |= dm9000_reg_read(DM9000_VIDH) << 8;

id_val |= dm9000_reg_read(DM9000_PIDL) << 16;

id_val |= dm9000_reg_read(DM9000_PIDH) << 24;

if (id_val == DM9000_ID)

{

printf("dm9000 is found !\n");

return ;

}

else

{

printf("dm9000 is not found !\n");

return ;

}

}

void dm9000_init()

{

u32 i;

//设置片选

cs_init();

//复位设备

dm9000_reset();

//捕获dm9000

dm9000_probe();

//MAC初始化

//Program operating register, only internal phy supported

dm9000_reg_write(DM9000_NCR, 0x0);

//TX Polling clear

dm9000_reg_write(DM9000_TCR, 0);

//Less 3Kb, 200us

dm9000_reg_write(DM9000_BPTR, BPTR_BPHW(3) | BPTR_JPT_600US);

// Flow Control : High/Low Water

dm9000_reg_write(DM9000_FCTR, FCTR_HWOT(3) | FCTR_LWOT(8));

//SH FIXME: This looks strange! Flow Control

dm9000_reg_write(DM9000_FCR, 0x0);

//Special Mode

dm9000_reg_write(DM9000_SMCR, 0);

//clear TX status

dm9000_reg_write(DM9000_NSR, NSR_WAKEST | NSR_TX2END | NSR_TX1END);

// Clear interrupt status

dm9000_reg_write(DM9000_ISR, ISR_ROOS | ISR_ROS | ISR_PTS | ISR_PRS);

//填充MAC地址

for (i = 0; i < 6; i++)

dm9000_reg_write(DM9000_PAR+i, macc_addr[i]);

//激活DM9000

dm9000_reg_write(DM9000_RCR, RCR_DIS_LONG | RCR_DIS_CRC | RCR_RXEN);

//Enable TX/RX interrupt mask

dm9000_reg_write(DM9000_IMR, IMR_PAR);

}

2.4 DM9000发送函数

void dm9000_tx(u8 *data,u32 length)

{

u32 i;

//禁止中断

dm9000_reg_write(DM9000_IMR,0x80);

//写入发送数据的长度

dm9000_reg_write(DM9000_TXPLL, length & 0xff);

dm9000_reg_write(DM9000_TXPLH, (length >> 8) & 0xff);

//写入待发送的数据

DM_ADD = DM9000_MWCMD;

for(i=0;i

{

DM_DAT = data[i] | (data[i+1]<<8);

}

//启动发送

dm9000_reg_write(DM9000_TCR, TCR_TXREQ);

//等待发送结束

while(1)

{

u8 status;

status = dm9000_reg_read(DM9000_TCR);

if((status&0x01)==0x00)

break;

}

//清除发送状态

dm9000_reg_write(DM9000_NSR,0x2c);

//恢复中断使能

dm9000_reg_write(DM9000_IMR,0x81);

}

2.5 DM9000接收函数

#define PTK_MAX_LEN 1522

u32 dm9000_rx(u8 *data)

{

u8 status,len;

u16 tmp;

u32 i;

//判断是否产生中断,且清除

if(dm9000_reg_read(DM9000_ISR) & 0x01)

dm9000_reg_write(DM9000_ISR,0x01);

else

return 0;

//空读

dm9000_reg_read(DM9000_MRCMDX);

//读取状态

status = dm9000_reg_read(DM9000_MRCMD);

//读取包长度

len = DM_DAT;

//读取包数据

if(len

{

for(i=0;i

{

tmp = DM_DAT;

data[i] = tmp & 0x0ff;

data[i+1] = (tmp>>8)&0x0ff;