1: ARM3级流水线

由ARM7-TDMI-S技术参考手册P2可知,ARM的流水线结构为:

取指----->译码------>执行

ARM代码: PC PC- 4 PC - 8

0x1008 0x1004 0x1000

在此页,还注明,PC是指向被取指的指令,而不是正在执行的指令。(也就是说在此 PC值为0x1008 ?)

2: 当发生BL跳转前,会在寄存器 R14 (即LR)中保存当前PC-4,即bl跳转指令的下一条指令的地址。所以在返回时只要 MOV pc,lr

3:中断

(1)当发生中断的时候,把是寄存器pc当前值存入LR(此时的LR是中断模式下的LR),所以返回时,应该是将LR-4赋值给PC。(0x1004)注:有些异常中断可能要将LR-8或LR赋值给PC。详细请仔细看ARM数据手册。

(2)当发生IRQ或FIQ后,系统要进入相应的异常模式进行处理,这些是由硬件实现的。

产生异常后,ARM核会做以下工作:

<1>. 将当前的地址加4或者加8存到LR寄存器里,即把当前状态下下一条指令的地址存入LR

<2>. 将CPSR复制到SPSR,

<3>. 然后将异常模式的状态强制写入CPSR

<4>. 强制PC从相关的异常向量处取指!!

中断结束后:

1. 将SPSR复制回CPSR

2. 开中断

3. 返回原程序,LDR PC,LR

4:因为每个模式下面都有LR,所以当返回原来模式时,原来模式下的LR并没有被破坏。

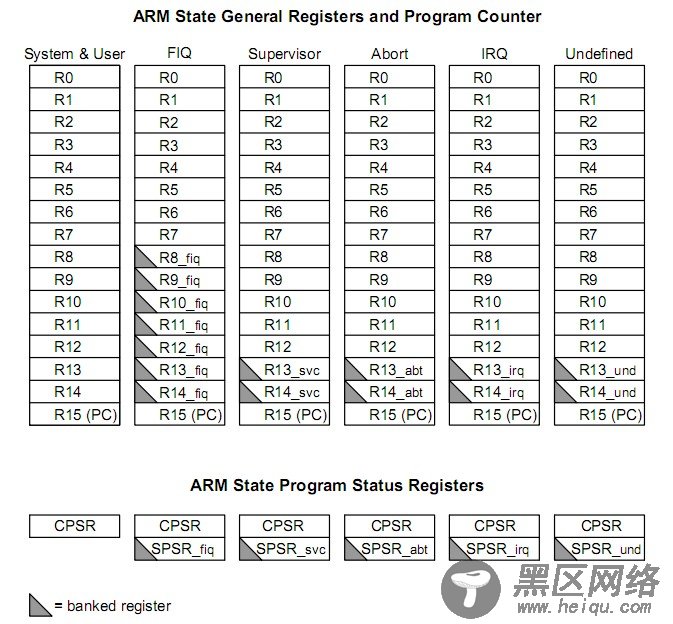

上图为ARM处理器的各个状态下的寄存器示意图