类似之前的执行方式,得到如下原始运行结果

hehaodeMacBook-Pro:build hehao$ ./Simulator ../test-inclass/add.riscv Program exit from an exit() system call ------------ STATISTICS ----------- Number of Instructions: 876 Number of Cycles: 1183 Avg Cycles per Instrcution: 1.3505 Branch Perdiction Accuacy: 0.4639 (Strategy: Always Not Taken) Number of Control Hazards: 124 Number of Data Hazards: 433 Number of Memory Hazards: 58 ----------------------------------- hehaodeMacBook-Pro:build hehao$ ./Simulator ../test-inclass/mul-div.riscv Program exit from an exit() system call ------------ STATISTICS ----------- Number of Instructions: 901 Number of Cycles: 1208 Avg Cycles per Instrcution: 1.3407 Branch Perdiction Accuacy: 0.4639 (Strategy: Always Not Taken) Number of Control Hazards: 124 Number of Data Hazards: 463 Number of Memory Hazards: 58 ----------------------------------- hehaodeMacBook-Pro:build hehao$ ./Simulator ../test-inclass/n\!.riscv Program exit from an exit() system call ------------ STATISTICS ----------- Number of Instructions: 1112 Number of Cycles: 1525 Avg Cycles per Instrcution: 1.3714 Branch Perdiction Accuacy: 0.4661 (Strategy: Always Not Taken) Number of Control Hazards: 189 Number of Data Hazards: 515 Number of Memory Hazards: 34 ----------------------------------- hehaodeMacBook-Pro:build hehao$ ./Simulator ../test-inclass/qsort.riscv Program exit from an exit() system call ------------ STATISTICS ----------- Number of Instructions: 19427 Number of Cycles: 25328 Avg Cycles per Instrcution: 1.3038 Branch Perdiction Accuacy: 0.4701 (Strategy: Always Not Taken) Number of Control Hazards: 1363 Number of Data Hazards: 14156 Number of Memory Hazards: 3174 ----------------------------------- hehaodeMacBook-Pro:build hehao$ ./Simulator ../test-inclass/simple-function.riscv Program exit from an exit() system call ------------ STATISTICS ----------- Number of Instructions: 886 Number of Cycles: 1197 Avg Cycles per Instrcution: 1.3510 Branch Perdiction Accuacy: 0.4639 (Strategy: Always Not Taken) Number of Control Hazards: 126 Number of Data Hazards: 438 Number of Memory Hazards: 58 -----------------------------------从这些原始数据中可以分析得到要求的结果,下面会对这些结果进行总结。

4.2.2 动态执行的指令数 程序名 执行的指令数add.riscv 876

mul-div.riscv 901

n!.riscv 1112

qsort.riscv 19427

simple-function.riscv 886

4.2.3 执行周期数和平均CPI 程序名 执行周期数 平均CPI

add.riscv 1183 1.3505

mul-div.riscv 1208 1.3407

n!.riscv 1525 1.3714

qsort.riscv 25328 1.3038

simple-function.riscv 1197 1.3510

可以发现,对于各种类型的程序,本模拟器流水线实现的平均CPI在1.33左右,和单周期相比能实现大约3.76倍的指令吞吐量。

4.2.4 不同类型的冒险统计 程序名 数据冒险 控制冒险 内存访问冒险add.riscv 433 124 58

mul-div.riscv 463 124 58

n!.riscv 515 189 34

qsort.riscv 14156 1363 3174

simple-function.riscv 438 126 58

五、其它内容 5.1 分支预测模块

分支预测模块是一个相对比较独立的模块,因此单独实现为BranchPredictor类。BranchPredictor类需要指定一个分支预测有关的策略,并保存与这个策略有关的数据结构。本模拟器实现了如下几种策略

策略名称 策略说明NT Always Not Taken

AT Always Taken

BTFNT Back Taken Forward Not Taken

BPB Branch Prediction Buffer

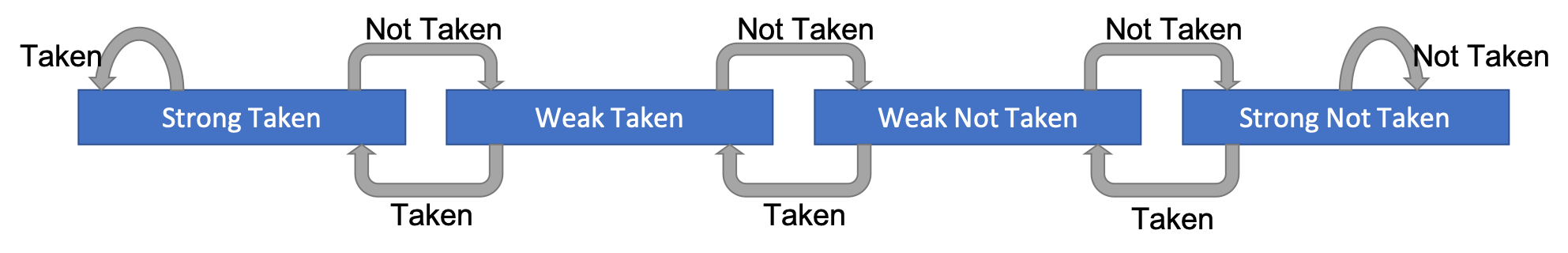

其中,Branch Prediction Buffer采用"Computer Organization and Design: Hardware/Software Interface"中所介绍的四状态,两位历史信息的方法。具体地说,使用内存后12位作为索引维护一个长度为4096的直接映射高速缓存,用于存储分支指令的地址。对于一个缓存条目,其状态为以下四个状态之一:Strong Taken, Weak Taken, Weak Not Taken, Strong Not Taken. 状态转换图如下