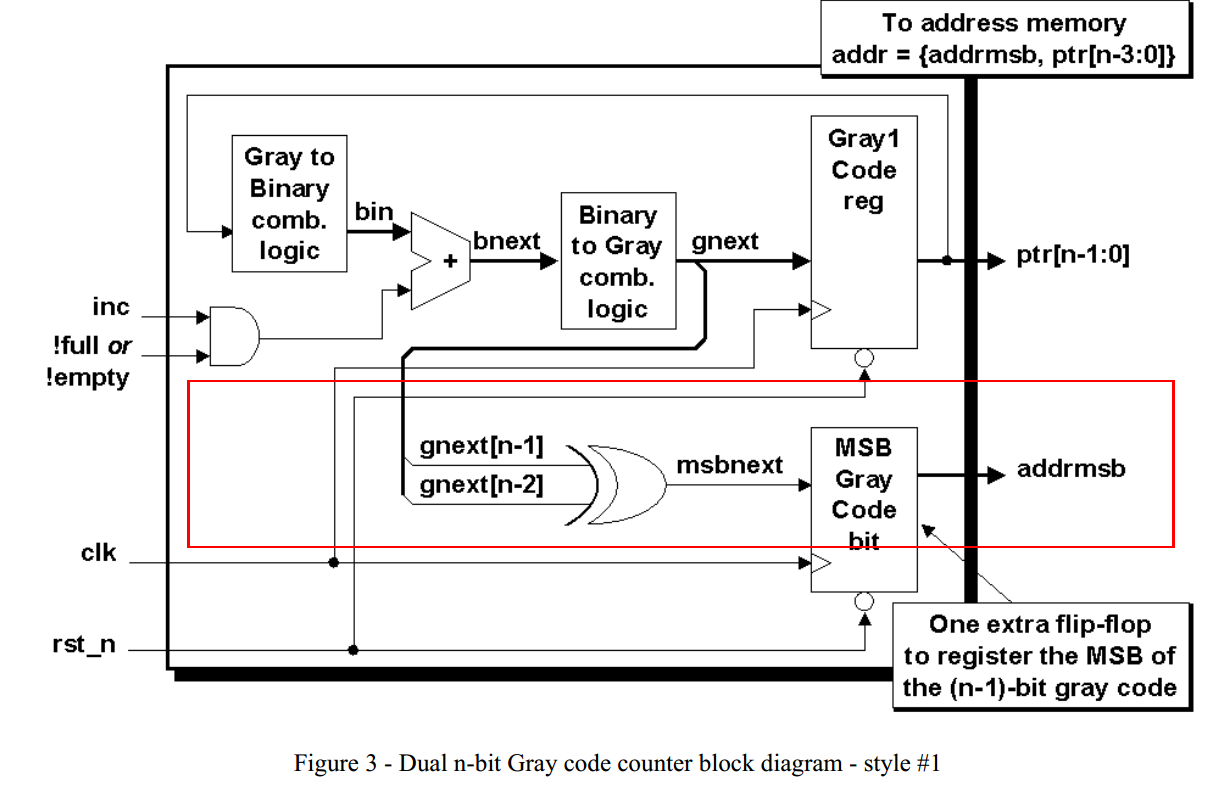

wire [n-1:0] bnext,gnext;

wire inc,full; // 写时钟域的格雷码转换器

reg [n-1:0] ptr; //输出的n位格雷码

reg [n-1:0] bin;

integer i;

assign bnext = bnext+(inc && !full)?1:0;

assign gnext = (bnext>>1) ^ bnext; //二进制转格雷码

always @(posedge clk or negedge rst_n) begin

if(rst_n==1'b0) {ptr,bin}<=0;

else {ptr,bin} <={gnext,bnext};

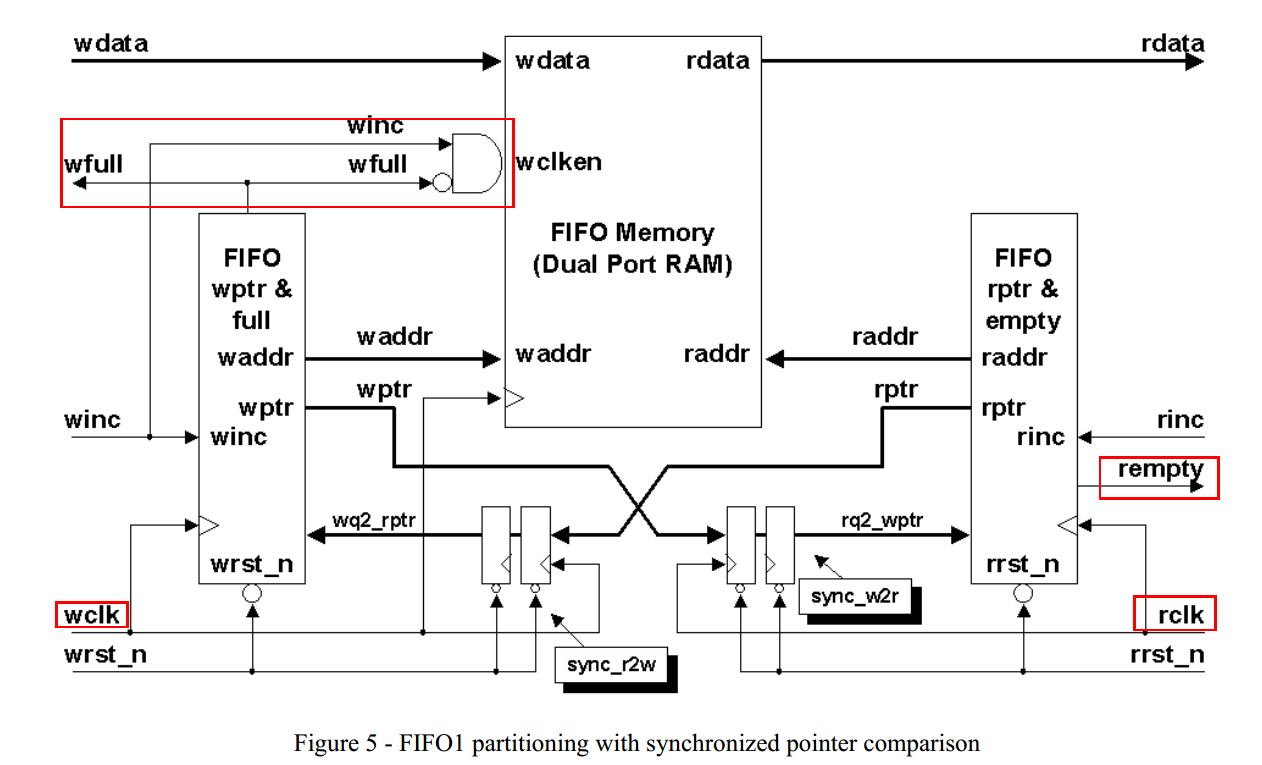

end 4. fifo结构图

空标志位在读时钟域产生;满标志位在写时钟域产生。

5.1 空标志位地址比实际地址增加一位。

读时钟域的格雷码读地址 与 同步过来的格雷码写地址相同,说明满

assign rempty_val = (rgraynext == rq2_wptr); // 读时钟域的格雷码读地址 与 同步过来的格雷码写地址相同,说明满always @(posedge rclk or negedge rrst_n) // 读时钟

if (!rrst_n) rempty <= 1'b1;

else rempty <= rempty_val; 5.2 满标志位

地址比实际地址增加一位。