存储器层次结构 存储技术

计算机技术的成功很大程度来源于存储技术的巨大进步。早期的电脑甚至没有磁盘。现在电脑上的磁盘都已经按T算了。

随机访问存储器(Random-Access Memory, RAM)随机访问存储器(Random-Access Memory, RAM)分两类:

静态的:SRAM,高速缓存存储器,既可以在CPU,也可以在片下。

动态的:DRAM,用于主存或者图形系统帧缓冲区。

通常情况下,SRAM的容量都不会太大,而相比之下DRAM容量可以大得离谱。

静态RAMSRAM将每个位存储在一个双稳态存储器单元里,每个单元用一个六晶体管电路实现。

这种电路有一个属性,它可以无限期地保持两个不同的状态的其中一个,其他状态都是不稳定的。

如上图,它能稳定在左态和右态,如果处于不稳定状态,它就像钟摆一样立刻变成两种稳态的其中一种。

也因为它的双稳态特性,即使有干扰,等到干扰消除,电路就能恢复成稳定值。

动态RAMDRAM的每个存储是一个电容和访问晶体管组成,每次存储相当于对电容充电。

该电容很小,大约只有30毫微微法拉。

因为每个存储单元比较简单,DRAM可以造的非常密集。但它对干扰非常敏感,被干扰后不会恢复。

因此它必须周期性地读出重写来刷新内存的每一位。或者使用纠错码来纠正任何单个错误。

两者总结

DRAM芯片内的每一个单元被叫做超单元。

在芯片内,总共有\(d\) 个超单元,它们被排列成一个\(r \times c\) 大小的矩阵,也就是说\(d = r \times c\),每个超单元都可以用类似\((i, j)\) 之类的地址定位

而每个超单元则是由\(w\) 个DRAM单元组成。因此一个DRAM芯片可以存储\(dw\) 位的信息。

上图是一个\(16 \times 8\) 的DRAM芯片的组织。

首先由两个addr引脚依次传入行地址i 和列地址j 。每个引脚携带一个信号。由于这是\(4 \times 4\) 的矩阵,因此两个就够了。

然后定位到\((i, j)\) ,将该地址的超单元信息传出去。

信息是由引脚data 传出去的。由于一个超单元里有8个DRAM单元,因此使用了8个引脚

每个DRAM芯片被连接到一个内存控制器。该控制器可以读入或者读出\(w\) 位的数据。

整个读出过程是这样的:

内存控制器发送行地址\(i\) 到DRAM

内存控制器发送行地址\(j\) 到DRAM

DRAM发送\((i, j)\) 的内容作为响应

其中行地址被称为\(RAS(Row \space Access \space Strobe \space 行访问选通脉冲)\) ,列地址被称为\(CAS(Column \space Access \space Strobe \space 行访问选通脉冲)\) 。

两个地址是共用一个addr 引脚的。

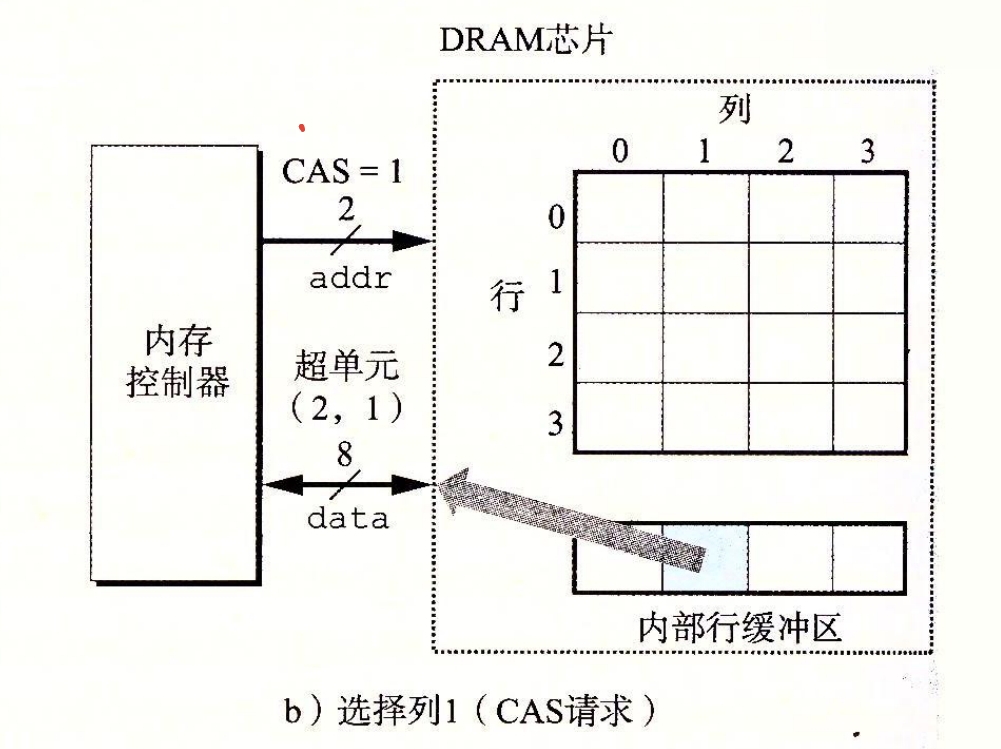

举个实际例子:

首先,内存控制器发送行地址2 ,DRAM做出的响应则是将一行的内容都复制到内部行缓冲区。

其次,内存控制器发动列地址1,DRAM做出的响应则是赋值行缓冲区的1列中的8位,然后发送到内存控制器。

将DRAM设计成矩阵的一个原因是降低芯片地址上的引脚数量,而缺点是必须分两步分发地址,增加访问时间。

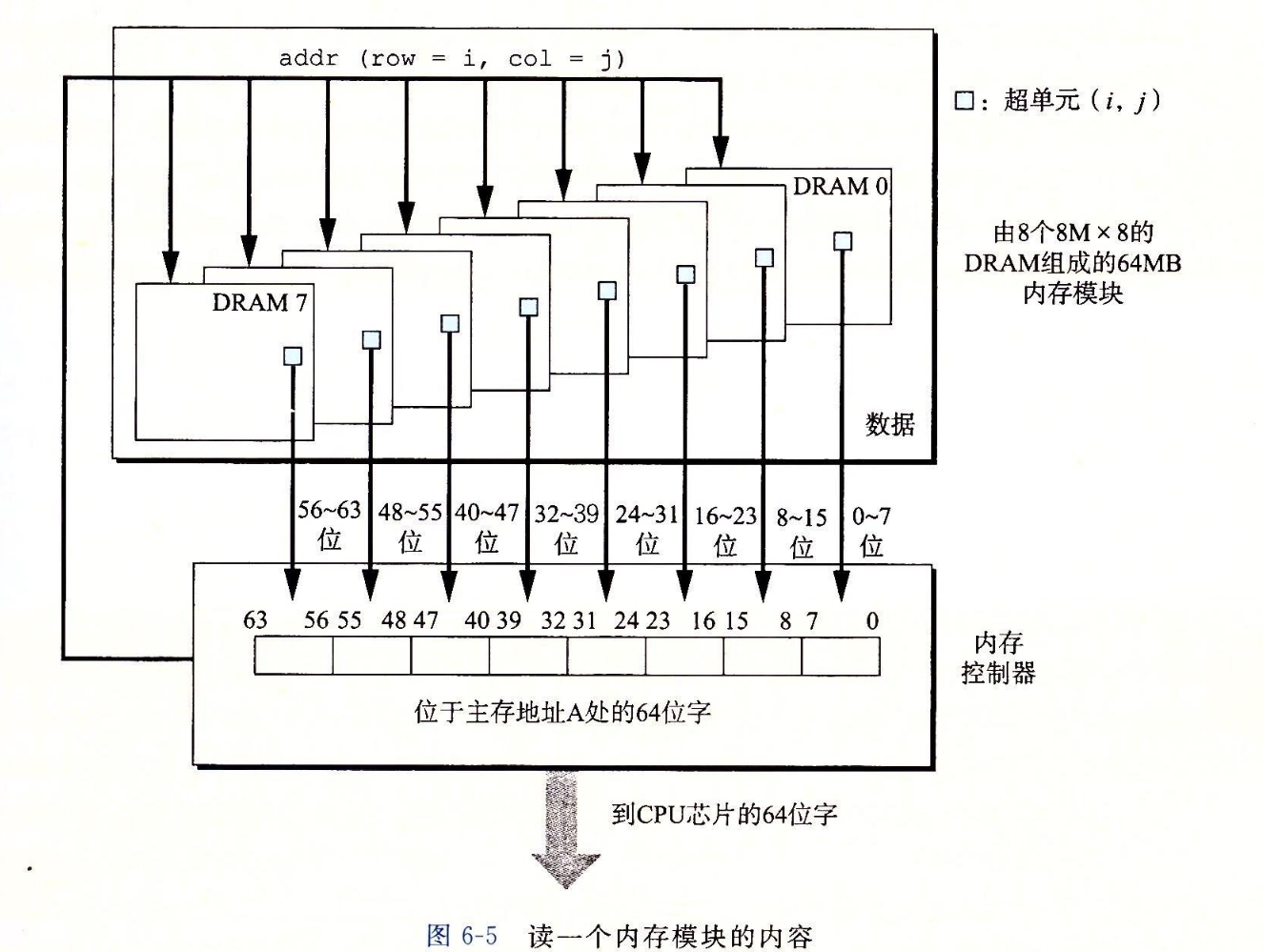

内存模块DRAM芯片封装在内存模块中,插到主板的拓展槽上。

看下图:

整个读取过程是这样的:

首先,内存控制器将一个内存地址翻译成一个超单元地址\((i, j)\)

内存控制器将地址广播到每一个DRAM芯片上。

每一块DRAM芯片作出响应,传出一个8位的字作为1个字节.

电路收集这些信息,将其合并成64位的字,再将信息返回给内存控制器

增强的DRAM实际上就是为了迎合需求,对普通的DRAM进行特定的优化以满足需求。

快页模式(FPM DRAM):与传统的DRAM不同的地方在于,它可以一个RAS之后接过多个CAS,即可以连续的读取同行的数据,不需要重复发送RAS

扩展数据输出DRAM(EDO DRAM):实际上就是FPM DRAM的增强形式,他让CAS信号可以发送地更紧密一些。

同步DRAM(SDRAM):传统的DRAM是异步传输地址的。而这个利用一些技术达成了同步传输地址,它能比传统的异步存储器更快地输出单元信息。

双倍数据速率同步DRAM(DDR SDRAM):对SDRAM的一种增强,能使DRAM速度翻倍。

视频RAM(VRAM):它用于图形系统的帧缓冲区中。

非易失性存储器如果断电,DRAM和SRAM会丢失它们的信息,他们属于易失性存储器。

因此,非易失性存储器就是关电之后仍然保存它们的信息。他们统称只读存储器\(Read-only \space Memory \space,ROM\) 。

它们是以能够被重编程的次数和重编程的机制来区分的。

PROM\((\space Programmable \space ROM \space)\) 可编程ROM:只能被编程一次,PROM的每个存储器单元有一种熔丝,只能用高电流熔断一次。

可擦写可编程ROM\((Erasable \space Programmable \space ROM, \space EPROM\)) :可反复擦写编程1000次以上。

电子可擦除PROM\((Electrically \space Erasable \space PROM, \space EEPROM)\) :可擦写编程的数量级为\(10^5\) 次。

闪存\((flash \space memory)\) :非易失性存储器,基于EEPROM。

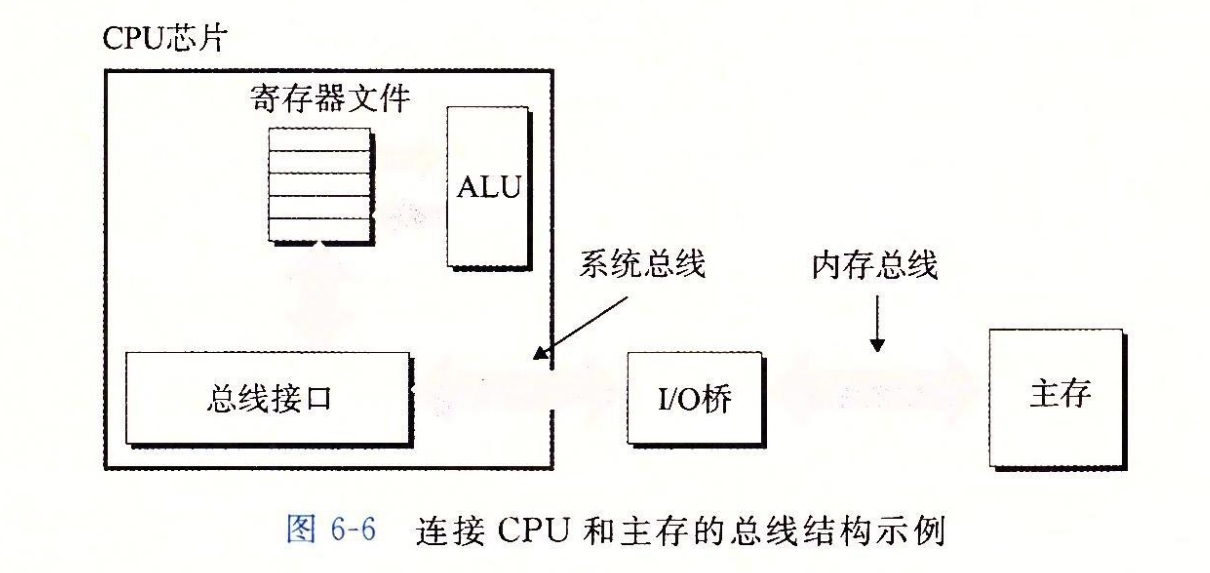

访问主存数据流在处理器和DRAM主存之间的来来回回是通过总线(bus)的共享电子电路实现的。

数据传送的步骤被称为总线事务,读事务从主存传送数据到CPU,写事务从CPU传送数据到主存。

总线是一行并行的导线,能携带地址,数据和控制信号。

数据和地址信号能否共享同一组导线取决于总线的设计。且两台以上的设备也能共享总线。

总线上的控制信号会同步事务,且能标识出事务类型。

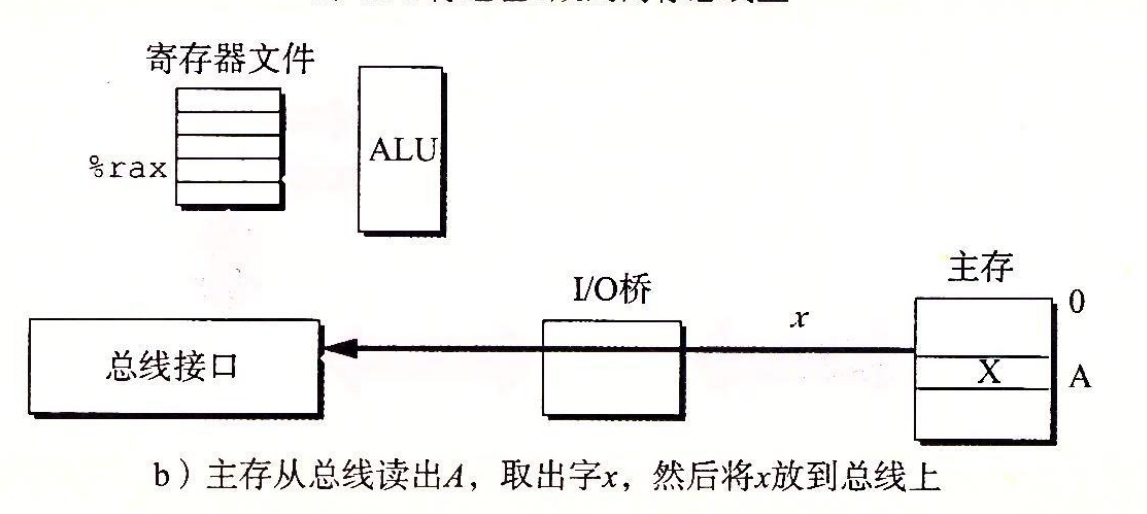

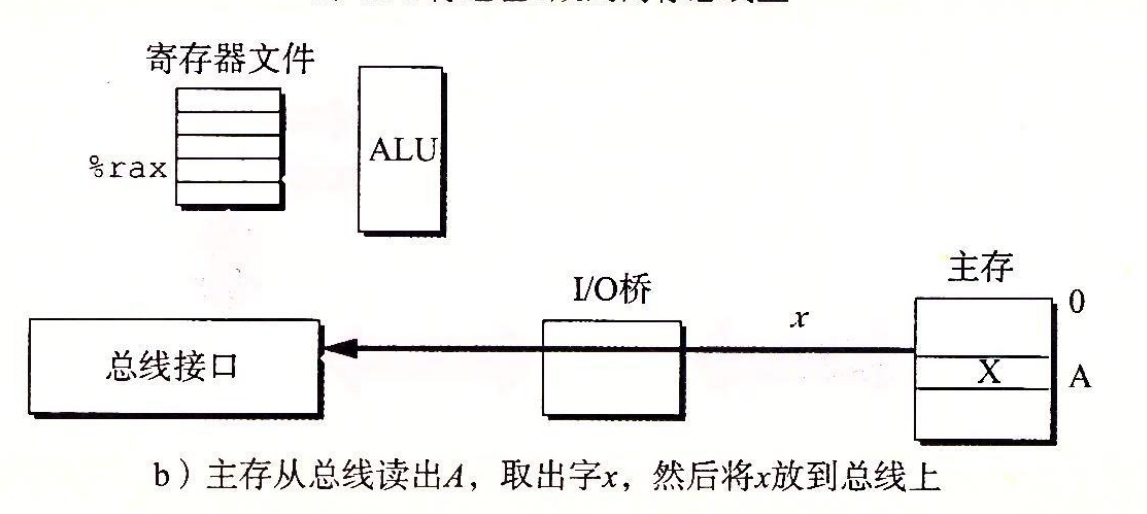

考虑如下操作时会发生什么:

movq A, %rax

CPU将地址A放到系统总线上,I/O桥把信号传到内存总线

主存发现了内存总线上的地址,从内存总线中读取地址,再从DRAM中将数据x放到内存总线上

I/O桥把内存总线上的信号翻译成系统总线信号,再放上系统总线传递。最后CPU发现了数据的传递,从总线上读取数据,并将数据复制到寄存器%rax 。

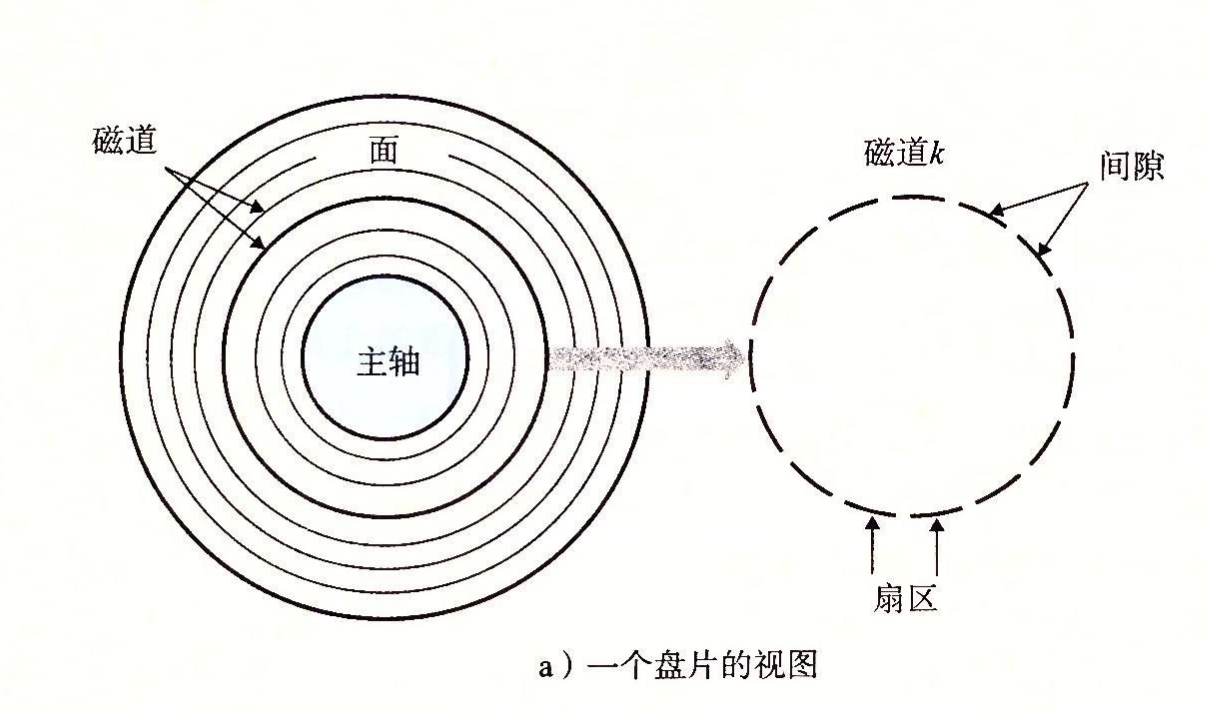

磁盘是被大量使用来存储信息的设备。

磁盘构造磁盘由盘片构成,每个盘片有两面,都称为表面,表面覆盖着磁性记录材料。

盘片中央有一个可以旋转的主轴,它能使盘片以固定的旋转速率旋转,通常是5400~15000转每分钟。

通常磁盘包含一个或者多个这样的盘片,并封装在一个密封的容器内。

上图展示了一个典型的磁盘表面的结构。

每个表面是由一组称为磁道的同心圆组成的。每个磁道被划分成为一组扇区。每个扇区会有相等数量的数据位。

扇区之间由一些间隙隔开,间隙间不存储数据位,间隙存储用来标识扇区的格式化位。